What is a D-Type Flip Flop?

- A D-Type (Data or Delay) flip flop is a fundamental component in sequential digital circuits

- It is a type of bistable circuit, meaning it has two stable states (0 and 1)

- It is used to store the state of 1 bit of data

- It is a synchronous component, meaning it only changes state based on a clock signal (specifically the “edge” of the signal)

Components

- Data Input (): The value (0 or 1) that we want to store

- Clock Input (): Controls when the data is stored

- Output (): The currently stored value

- Inverted Output (): The opposite of (sometimes labelled as NOT Q)

D-Type Flip Flop Symbol

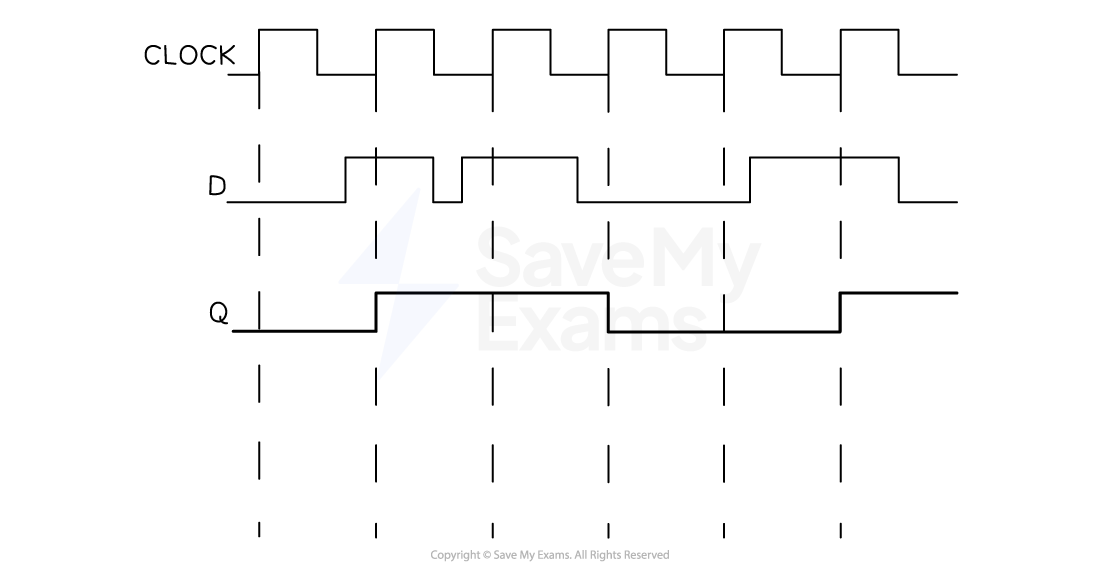

Operation (Positive Edge Triggering)

- The D-Type flip flop is positive edge triggered

- This means it only “looks” at the input at the precise moment the Clock signal changes from Low (0) to High (1) (the rising edge)

- Rising Edge occurs: The circuit checks the value of input

- If : Output becomes 1 (High)

- If : Output becomes 0 (Low)

- Latch: Between clock pulses, the value of remains constant (“latched”), effectively remembering the value even if changes in the meantime

Use Cases

- Register Memory: Used to create registers inside the CPU

- Counters: Used in digital clocks and timers

- Shift Registers: Used for serial-to-parallel conversion

- Data Storage: Fundamental for Static RAM (SRAM)

Examiner Tips and Tricks

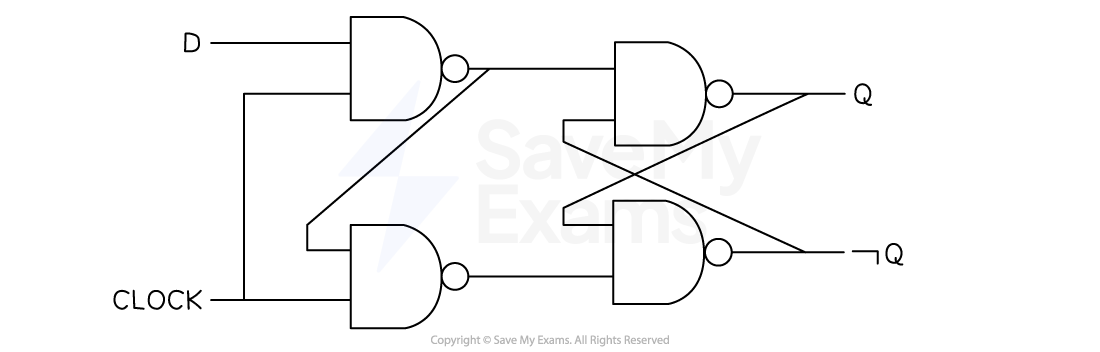

You will not be asked to recall the specific arrangement of logic gates that make up a D-type flip flop, as they can be constructed in various ways.

However, it is useful to know they are often built using NAND gates (AND gates with inverted outputs).

Internal Logic Gate Structure

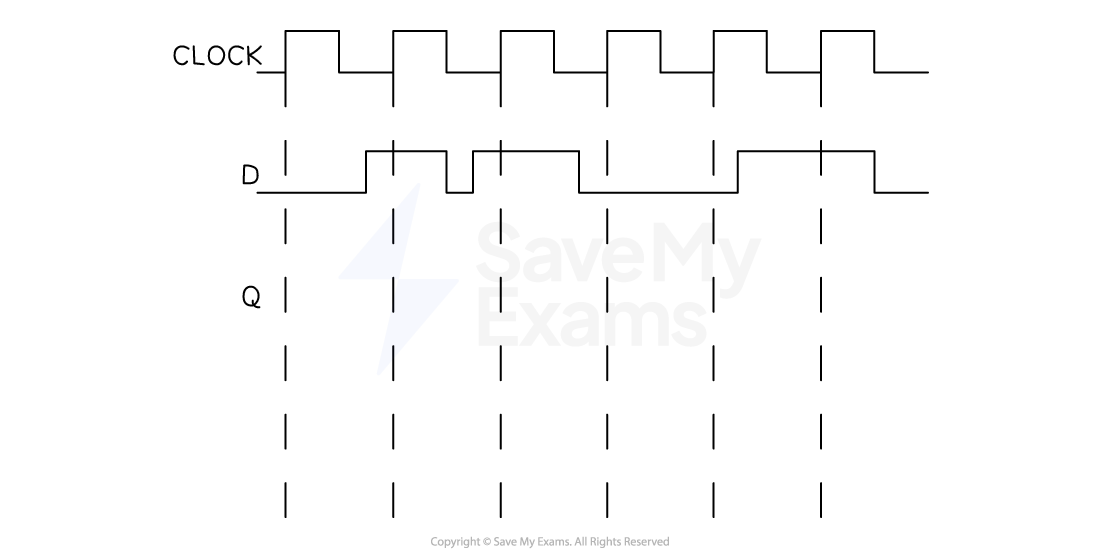

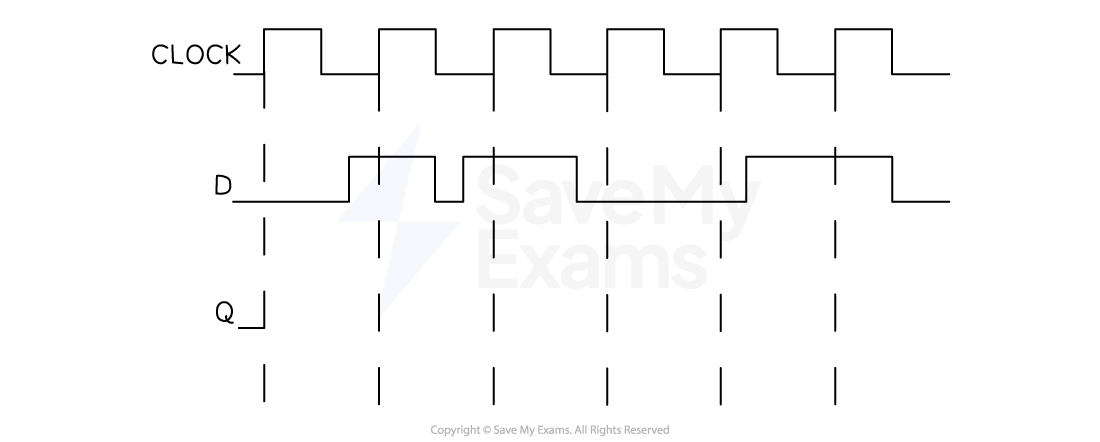

Worked Example

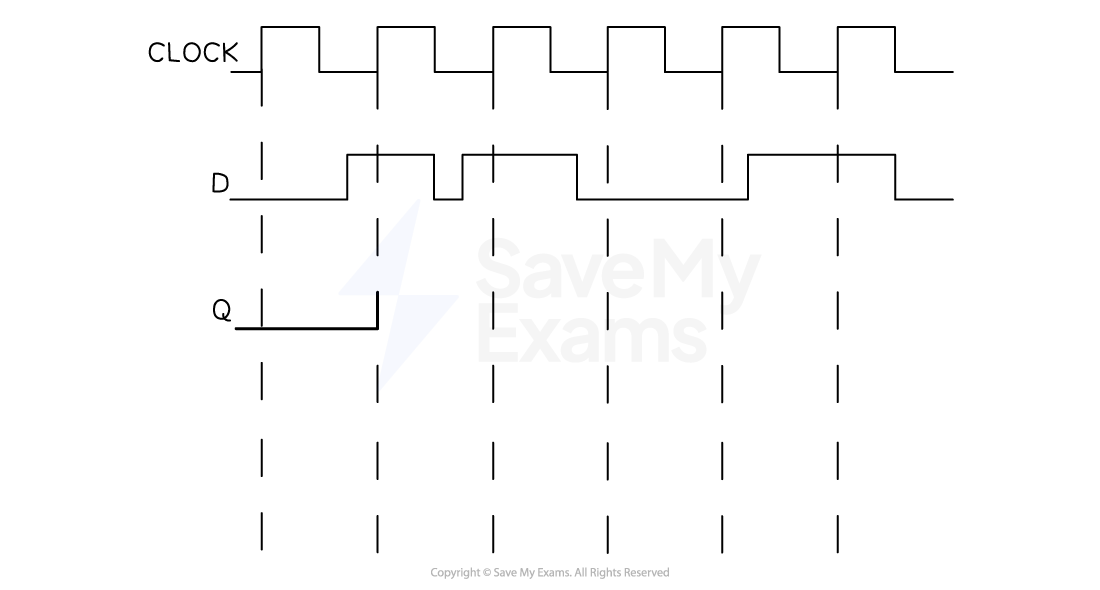

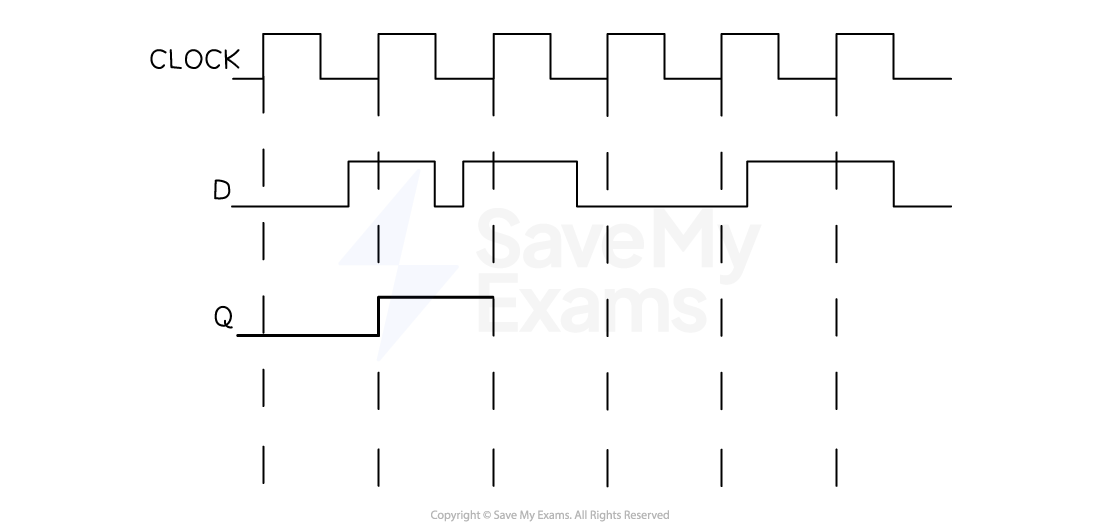

Question: Draw the output of the Flip Flop on the diagram below

Method:

- The output line should mirror the input , BUT it can only change when the clock signal changes from low to high (indicated by the dotted vertical lines)

- Step 1: Assume starts at the same state as (Low/0 in this case)

- Step 2: Draw the line from left to right. Do not change the level of until you hit a vertical dotted line

- Step 3: At the first dotted line, check . is Low, so remains Low.

- Step 4: At the second dotted line (rising edge), check . is now High, so becomes High.

- Step 5: is now “latched” at High. Even if changes in between, ignore it.

- Step 6: At the next dotted line, check . is still High, so remains High.

- Step 7: Continue this process until the end of the diagram.